Nhóm Amber: Giải thích toàn diện về bằng chứng không kiến thức

Nguồn gốc: Nhóm Amber

Nguồn gốc: Nhóm Amber

1. Giới thiệu

Bằng chứng không kiến thức cho phép một bên chứng minh tính xác thực cho bên khác mà không tiết lộ bất kỳ thông tin bổ sung nào. Do đó, nó có thể được sử dụng để bảo vệ quyền riêng tư và xác minh tính hợp lệ của các giao dịch trong khi ẩn tất cả các chi tiết. Điều quan trọng là các giao thức không có kiến thức nhất định phải thuận tiện để xác minh bằng chứng không có kiến thức, chẳng hạn như STARK và SNARK. Các giao thức này tạo ra các bằng chứng nhỏ hơn và việc xác minh các bằng chứng đó nhanh hơn nhiều. Điều này rất phù hợp với các chuỗi khối bị hạn chế về tài nguyên và đặc biệt quan trọng trong việc giải quyết các vấn đề về khả năng mở rộng trong ngành công nghiệp tiền điện tử. Ngoài ra, các trường hợp sử dụng khác của công nghệ không kiến thức bao gồm:

DID (ID phi tập trung) - để chứng minh rằng một tài khoản hoặc tổ chức có một số"tính năng"tính năng

, chẳng hạn như Sismo, Đợt đầu tiên

Quản trị cộng đồng - để bỏ phiếu ẩn danh và trường hợp sử dụng này có thể được mở rộng để quản trị thế giới thực sau khi được chứng minh và áp dụng rộng rãi

Báo cáo tài chính – Các thực thể có thể chứng minh việc tuân thủ các tiêu chí nhất định mà không cần tiết lộ số liệu tài chính chính xác

……

Tính toàn vẹn của dịch vụ đám mây - Giúp các nhà cung cấp dịch vụ đám mây thực hiện nhiệm vụ của họ tốt hơn

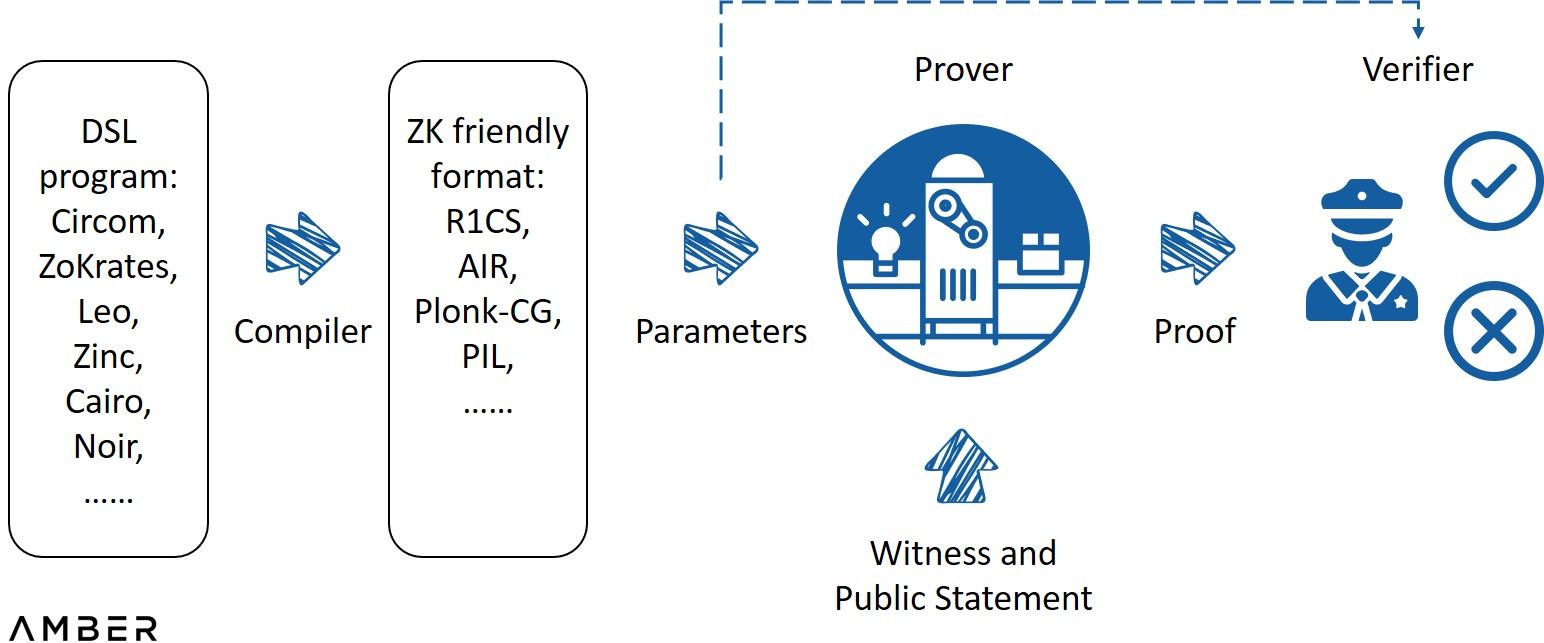

Một hệ thống không kiến thức điển hình

Mô tả hình ảnh

Nguồn: ZK Whiteboard Sessions - Module One, được viết bởi Giáo sư Dan Boneh

Một số hệ thống bằng chứng tuyệt vời đã được phát hành, chẳng hạn như Marlin, Plonky2, Halo2, v.v. Các hệ thống bằng chứng khác nhau có sự nhấn mạnh khác nhau vào các đặc điểm như kích thước của bằng chứng được tạo, thời gian cần thiết để xác minh và liệu có cần thiết lập đáng tin cậy hay không. Sau vài năm khám phá, có thể đạt được kích thước bằng chứng không đổi (hàng trăm byte) và thời gian xác minh ngắn (mili giây), bất kể câu lệnh phức tạp đến đâu.

Tuy nhiên, độ phức tạp của quy trình tạo bằng chứng gần như tuyến tính với kích thước của vòng lặp số học, do đó độ khó thậm chí có thể gấp hàng trăm lần so với nhiệm vụ ban đầu. Vì người châm ngôn ít nhất cần đọc và đánh giá vòng lặp, nên việc này có thể mất từ vài giây đến vài phút hoặc thậm chí hàng giờ. Chi phí điện toán cao và thời gian chứng minh dài là những trở ngại chính đối với tiến độ và ứng dụng quy mô lớn của công nghệ không kiến thức.

Tăng tốc phần cứng có thể giúp phá vỡ các nút thắt cổ chai. Các thuật toán hoặc tối ưu hóa phần mềm được sử dụng để phân phối nhiều tác vụ cho phần cứng phù hợp nhất, bổ sung cho nhau.

Báo cáo này nhằm mục đích giúp độc giả hiểu được bối cảnh thị trường, tác động của công nghệ không kiến thức đối với thị trường khai thác và các cơ hội tiềm năng. Báo cáo gồm ba phần:

phần kết

phần kết

tiêu đề cấp đầu tiên

2. Trường hợp sử dụng

Việc liệt kê các trường hợp sử dụng không có kiến thức sẽ giúp minh họa thị trường đang phát triển như thế nào. Bởi vì các loại khác nhau có nhu cầu khác nhau, việc cung cấp phần cứng cũng liên quan. Ở cuối phần này, chúng tôi cũng sẽ so sánh ngắn gọn ZKP và PoW (đặc biệt là đối với Bitcoin).

2.1 Chuỗi khối mới nổi và các yêu cầu khác biệt của nó

Các chuỗi khối mới nổi hiện nay sử dụng công nghệ không kiến thức là nhu cầu chính để tăng tốc phần cứng, có thể tạm chia thành các giải pháp mở rộng quy mô và chuỗi khối bảo vệ quyền riêng tư. Rollup hoặc Volition không có kiến thức thực hiện giao dịch ngoài chuỗi và gửi bằng chứng xác minh ngắn gọn thông qua chức năng "calldata". Chuỗi khối bảo vệ quyền riêng tư sử dụng ZKP để cho phép người dùng đảm bảo tính hợp lệ của các giao dịch được thực hiện mà không tiết lộ chi tiết giao dịch.

Các chuỗi khối này đánh đổi các thuộc tính như kích thước bằng chứng, thời gian xác minh và cài đặt đáng tin cậy bằng cách sử dụng các hệ thống bằng chứng khác nhau. Ví dụ: bằng chứng do Plonk tạo có kích thước bằng chứng không đổi (khoảng 400 byte) và thời gian xác minh (khoảng 6 mili giây), nhưng vẫn yêu cầu thiết lập đáng tin cậy chung. Ngược lại, Stark không yêu cầu thiết lập đáng tin cậy, nhưng kích thước bằng chứng (~80KB) và thời gian xác minh (~10 mili giây) của nó là dưới mức tối ưu và tăng theo kích thước vòng lặp. Các hệ thống khác cũng có ưu và nhược điểm. Sự đánh đổi giữa các hệ thống chứng minh này sẽ dẫn đến sự thay đổi "trọng tâm" của khối lượng tính toán.

Cụ thể, hệ thống bằng chứng hiện tại thường có thể được mô tả là PIOP (Bằng chứng tiên tri tương tác đa thức) + PCS (Lược đồ cam kết đa thức). Cái trước có thể được coi là một chương trình đã được thống nhất sử dụng bởi người chứng minh để thuyết phục người xác minh, trong khi cái sau sử dụng các phương pháp toán học để đảm bảo rằng chương trình không thể bị phá vỡ. Nó giống như PCS là một khẩu súng và PIOP là một viên đạn. Bên dự án có thể sửa đổi PIOP khi cần và có thể chọn trong số các PCS khác nhau.Georgios Konstantopoulos về Mô hình trong tác phẩm của ôngBáo cáo về tăng tốc phần cứng

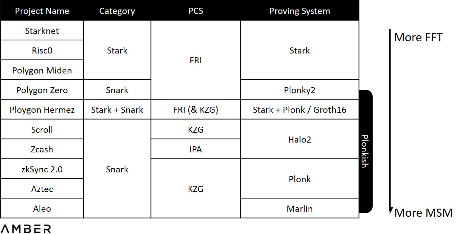

Như đã giải thích trong , thời gian cần thiết để tạo ra một bằng chứng chủ yếu phụ thuộc vào hai loại nhiệm vụ tính toán: MSM (Thuật toán nhân đa vô hướng) và FFT (Biến đổi Fourier nhanh). Tuy nhiên, thay vì sử dụng các tham số cố định, việc thiết lập các PIOP khác nhau và chọn từ các PCS khác nhau sẽ dẫn đến các phép tính FFT hoặc MSM khác nhau. Lấy Stark làm ví dụ, PCS mà Stark sử dụng là FRI (Bằng chứng tương tác tiệm cận mã Fast Reed-Solomon), dựa trên mã Liso, chứ không phải đường cong elip được sử dụng bởi KZG hoặc IPA, vì vậy nó hoàn toàn độc lập trong toàn bộ quy trình tạo bằng chứng.MSM có liên quan. Chúng tôi đã sắp xếp sơ bộ khối lượng tính toán của các hệ thống bằng chứng khác nhau trong bảng dưới đây. Cần lưu ý rằng 1) rất khó để ước tính khối lượng tính toán chính xác của toàn bộ hệ thống; 2) bên dự án thường sửa đổi hệ thống khi cần thiết trong quá trình triển khai .

Số tiền tính toán của các hệ thống bằng chứng khác nhau

Tình huống trên sẽ khiến các bên dự án có các tùy chọn loại phần cứng của riêng họ. GPU (Bộ xử lý đồ họa) hiện đang được sử dụng rộng rãi nhất do nguồn cung lớn và dễ phát triển. Ngoài ra, cấu trúc đa lõi của GPU rất thuận tiện cho việc tính toán MSM song song. Tuy nhiên, FPGA (Field Programmable Gate Arrays) có thể xử lý FFT tốt hơn, chúng tôi sẽ trình bày chi tiết trong Phần II. Các dự án sử dụng Stark, chẳng hạn như Starknet và Hermez, có thể yêu cầu FPGA nhiều hơn.

Một kết luận khác được rút ra từ những điều trên là công nghệ này vẫn đang ở giai đoạn đầu và thiếu các giải pháp tiêu chuẩn hóa hoặc chiếm ưu thế. Cũng có thể còn quá sớm để sử dụng đầy đủ ASIC (mạch tích hợp dành riêng cho ứng dụng) dành riêng cho các thuật toán cụ thể. Vì vậy, các nhà phát triển đang khám phá một nền tảng trung gian, mà chúng tôi sẽ giải thích thêm sau.

2.2 Xu hướng và mô hình mới

2.2.1 Các câu lệnh phức tạp hơnDựa trên các trường hợp sử dụng được liệt kê ở phần đầu, chúng tôi hy vọng kiến thức không có nhiều ứng dụng hơn trong ngành mã hóa và thế giới thực, đồng thời cho phép các bằng chứng phức tạp hơn, một số trong số đó thậm chí không phải tuân thủ hệ thống bằng chứng hiện tại. Thay vì sử dụng PIOP và PCS, bên dự án có thể phát triển các nguyên mẫu mới phù hợp nhất với họ. Và trong các lĩnh vực khác như MPC (tính toán đa bên an toàn), việc áp dụng các giao thức không kiến thức trong một số tác phẩm sẽ cải thiện đáng kể tiện ích của nó. Ethereum gần đây cũng có kế hoạch tổ chức Proto-DankshardingLễ thiết lập đáng tin cậy KZGTrong tương lai, chúng tôi dự định triển khai thêm phiên bản đầy đủ của Danksharding để xử lý lấy mẫu tính khả dụng của dữ liệu. Tổng hợp thậm chí lạc quanCó thể áp dụng ZKP trong tương lai

Để nâng cao tính bảo mật và rút ngắn thời gian xử lý tranh chấp.Mặc dù nhiều người có thể coi kiến thức không có dữ liệu là một lĩnh vực riêng biệt trong ngành công nghiệp tiền điện tử nói chung, nhưng chúng tôi tin rằng kiến thức không có dữ liệu nên được xem như một công nghệ giải quyết nhiều điểm khó khăn trong ngành.

Mặt khác, để cung cấp dịch vụ cho các hệ thống và khách hàng khác nhau, khả năng tăng tốc phần cứng sẽ linh hoạt và đa năng hơn trong tương lai.

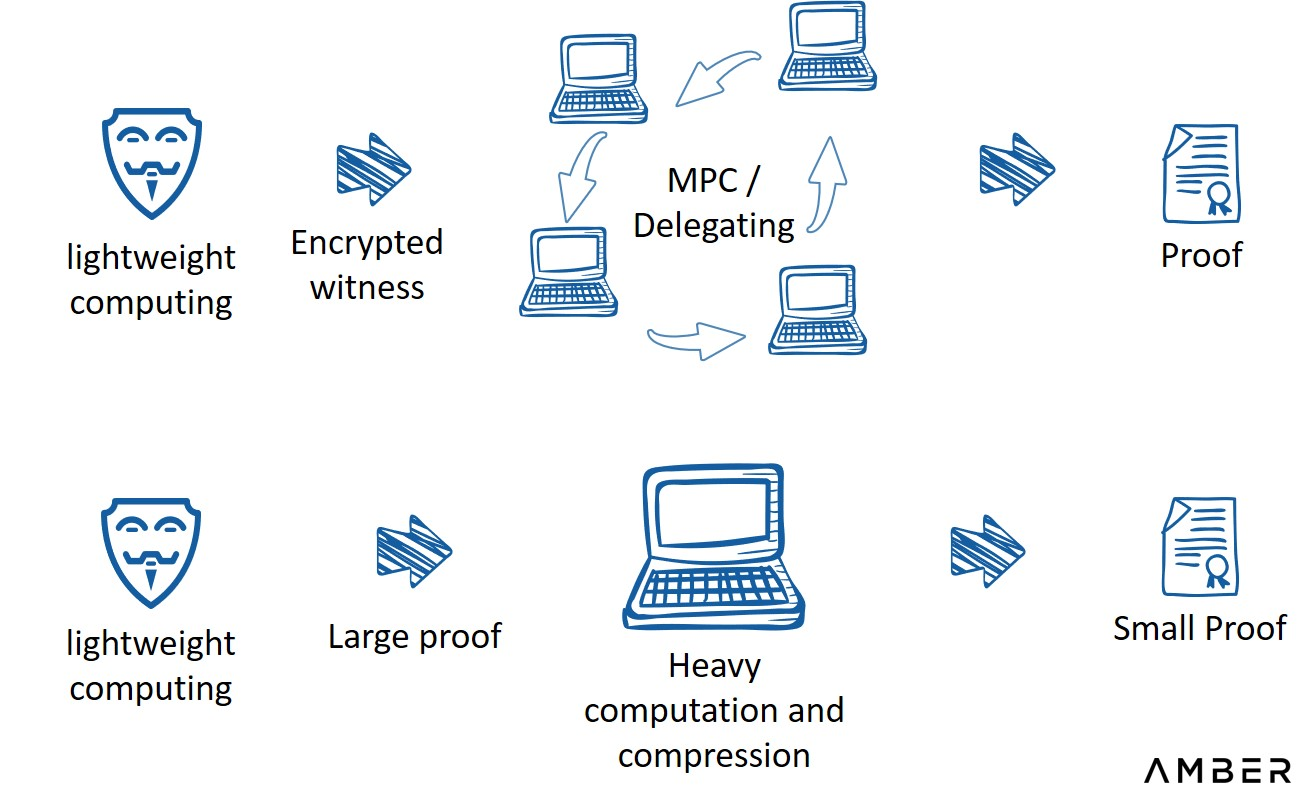

2.2.2 Bằng chứng về thế hệ cục bộZKP để bảo vệ quyền riêng tư và ZKP để nén thông tin có sự khác biệt rõ ràng về cấu trúc. Để ẩn chi tiết giao dịch, một số số ngẫu nhiên có liên quan đến quá trình chứng minh. Người dùng cần tạo bằng chứng cục bộ, nhưng hầu hết người dùng không có phần cứng nâng cao. Tệ hơn nữa, nếu hầu hết các dapp vẫn là Ứng dụng web, thì cần phải tạo bằng chứng trong trình duyệt, điều này sẽ mất nhiều thời gian hơn để chứng minh. Ví dụ: khi Manta cố gắng xây dựng một chứng minh hiệu suất cao cho WASM, họ nhanh chóng nhận ra rằng "WASM gây ra hình phạt cho người dùng về hiệu suất gấp 10-15 lần so với tốc độ xử lý gốc". Để giải quyết vấn đề này, Manta đã chọn trở thành nhà tài trợ và kiến trúc sư của ZPrize, một trong những cuộc thi tăng tốc ZKP lớn nhất và Manta đã thiết lập giải pháp tăng tốc WASMbài hát độc quyền

. Cung cấp phiên bản ứng dụng khách là một giải pháp đơn giản cho loại dapp này, nhưng nhu cầu tải xuống có thể khiến một số người dùng tiềm năng bị mất và ứng dụng khách không phù hợp với ví tiện ích mở rộng hiện tại hoặc các công cụ khác.Một giải pháp khác là thuê ngoài một phần việc tạo bằng chứng. Pratyush Mishra trình bày trong Hội nghị thượng đỉnh tri thức Zero lần thứ 7phương pháp này

Tạo bằng chứng thuê ngoài

Mô tả hình ảnh

Nguồn: 7th Zero Knowledge Summit, trình bày bởi Pratyush Mishra của Aleo

2.3 So sánh với khai thác PoW

Mặc dù có thể coi ZKP là một dạng PoW mới và xem phần cứng tăng tốc như một loại máy khai thác mới, thế hệ ZKP về cơ bản khác với khai thác PoW về mục đích và cấu trúc thị trường.

2.3.1 Cạnh tranh điện năng và tính toán tiện ích

Rates-are-Odds (Aleo):Để kiếm được phần thưởng khối và phí giao dịch, các công cụ khai thác Bitcoin lặp lại các nonce để tìm một giá trị băm đủ nhỏ, giá trị này thực sự chỉ liên quan đến sự đồng thuận. Ngược lại, việc tạo ZKP là một quá trình cần thiết để đạt được tiện ích thực tế như nén thông tin hoặc bảo vệ quyền riêng tư mà không chịu trách nhiệm về sự đồng thuận. Sự khác biệt này ảnh hưởng đến mô hình phân phối phần thưởng và tham gia rộng rãi tiềm năng của ZKP. Dưới đây chúng tôi liệt kê ba thiết kế hiện có để minh họa cách các công cụ khai thác sẽ phối hợp tạo ZKP.

Winner-Dominates(Polygon Hermez):Thiết kế mô hình kinh tế của Aleo gần giống nhất với Bitcoin và các giao thức PoW khác. Cơ chế đồng thuận PoSW (Bằng chứng ngắn gọn về công việc) của nó vẫn yêu cầu người khai thác tìm một giá trị ngẫu nhiên hiệu quả, nhưng quá trình xác minh chủ yếu dựa trên việc tạo ra nhiều lần bằng chứng SNARK, sử dụng các giá trị ngẫu nhiên và giá trị băm của gốc trạng thái làm đầu vào, và quá trình tiếp tục cho đến khi Giá trị băm bằng chứng được tạo trong một vòng nhất định đủ nhỏ. Chúng tôi gọi cơ chế giống như PoW này là mô hình Tỷ lệ là tỷ lệ cược, bởi vì số lượng xác minh có thể được xử lý trong một đơn vị thời gian xác định gần đúng xác suất nhận được phần thưởng. Trong mô hình này, những người khai thác tăng cơ hội nhận phần thưởng bằng cách tích trữ số lượng lớn máy tính.Polygon Hermez có một mô hình đơn giản hơn. theo họtài liệu công cộng

Party-Thresholds (Scroll):Từ góc độ nội dung, hai bên tham gia chính là người đặt hàng và người tổng hợp, người đặt hàng thu thập tất cả các giao dịch và xử lý trước chúng thành các lô L2 mới và người tổng hợp chỉ định mục đích xác minh của mình và cạnh tranh để tạo bằng chứng. Đối với một lô nhất định, người tổng hợp đầu tiên gửi bằng chứng sẽ kiếm được khoản phí do người đặt hàng trả. Các công cụ tổng hợp có cấu hình và phần cứng hiện đại có khả năng chiếm ưu thế bất kể phân phối địa lý, điều kiện mạng và chiến lược xác minh.

Scroll mô tả thiết kế của họ là "Gia công phần mềm bằng chứng lớp 2", trong đó những người khai thác đặt cược một lượng tiền điện tử nhất định sẽ được chọn tùy ý để tạo bằng chứng. Những người khai thác được chọn cần gửi bằng chứng trong thời gian quy định, nếu không, xác suất lựa chọn của họ cho kỷ nguyên tiếp theo sẽ bị hạ xuống. Tạo bằng chứng sai sẽ bị phạt tiền. Lúc đầu, Scroll có thể sẽ hoạt động với khoảng hơn chục công cụ khai thác để cải thiện tính ổn định và thậm chí chạy GPU của riêng nó. Và theo thời gian, họ có kế hoạch phi tập trung hóa toàn bộ quy trình. Chúng tôi sử dụng nút thời gian thực hiện phi tập trung này làm tham số để đo lường sự điều chỉnh trọng tâm của Scroll giữa hiệu quả và phi tập trung. Starkware cũng có thể thuộc loại này. Về lâu dài, chỉ những máy có khả năng hoàn thành bằng chứng kịp thời mới có thể tham gia tạo bằng chứng.Mỗi thiết kế phối hợp này có một trọng tâm khác nhau. Chúng tôi hy vọng Aleo có mức độ phân cấp cao nhất, Hermez có hiệu quả cao nhất và Scroll có rào cản tham gia thấp nhất.

Nhưng dựa trên thiết kế trên, một cuộc chạy đua vũ trang phần cứng không có kiến thức khó có thể xảy ra sớm.

2.3.2 Thuật toán tĩnh và thuật toán tiến hóa

Chúng tôi tin rằng so với thị trường PoW đơn giản và tĩnh, sự khác biệt của ZKP góp phần tạo nên cấu trúc thị trường phi tập trung và năng động hơn. Chúng tôi đề xuất coi việc tạo ZKP là một dịch vụ (một số công ty khởi nghiệp đặt tên cho nó là ZK-as-a-Service), trong đó việc tạo ZKP là một phương tiện để đạt được mục tiêu chứ không phải là mục đích cuối cùng. Mô hình mới này cuối cùng sẽ dẫn đến các mô hình kinh doanh hoặc doanh thu mới, chúng tôi sẽ trình bày chi tiết trong phần cuối cùng. Trước đó, chúng ta hãy xem xét nhiều giải pháp.

tiêu đề cấp đầu tiên

3. Giải pháp

CPU (bộ xử lý trung tâm) là chip chính trong máy tính đa năng và chịu trách nhiệm phân phối hướng dẫn cho các thành phần khác nhau trên bo mạch chủ. Tuy nhiên, do CPU được thiết kế để xử lý nhiều tác vụ một cách nhanh chóng, điều này làm hạn chế tốc độ xử lý nên GPU, FPGA và ASIC thường được sử dụng làm trợ lý khi xử lý các tác vụ đồng thời hoặc một số tác vụ cụ thể. Trong phần này, chúng tôi sẽ tập trung vào các đặc điểm, quy trình tối ưu hóa, hiện trạng và thị trường của chúng.

3.1 GPU: Phần cứng được sử dụng phổ biến nhất hiện naypippengerGPU ban đầu được thiết kế để điều khiển đồ họa máy tính và xử lý hình ảnh, nhưng cấu trúc song song của nó khiến nó trở thành lựa chọn tốt trong các lĩnh vực như thị giác máy tính, xử lý ngôn ngữ tự nhiên, siêu máy tính và khai thác PoW. GPU có thể tăng tốc MSM và FFT, đặc biệt là đối với MSM, bằng cách khai thác cái gọi là "

"thuật toán, quá trình phát triển GPU đơn giản hơn nhiều so với FPGA hay ASIC.

Ý tưởng tăng tốc trên GPU rất đơn giản: giảm tải các tác vụ đòi hỏi tính toán này từ CPU sang GPU. Các kỹ sư sẽ viết lại những phần này thành CUDA hoặc OpenCL. CUDA là một nền tảng điện toán song song và mô hình lập trình được Nvidia phát triển để điện toán chung trên GPU Nvidia. Đối thủ của CUDA là điện toán hỗn hợp do Apple và Khronos Group phát triển. Cung cấp OpenCL tiêu chuẩn, khiến người dùng không khỏi bỡ ngỡ giới hạn đối với GPU NVIDIA. Các mã này sau đó được biên dịch và chạy trực tiếp trên GPU. Để tăng tốc hơn nữa, các nhà phát triển cũng có thể:

(1) Để giảm chi phí truyền dữ liệu (đặc biệt là giữa CPU và GPU), hãy tối ưu hóa bộ nhớ bằng cách sử dụng càng nhiều bộ nhớ nhanh càng tốt và ít bộ nhớ chậm hơn.

(2) Để cải thiện việc sử dụng phần cứng và làm cho phần cứng hoạt động hết công suất tối đa có thể, hãy tối ưu hóa cấu hình thực thi bằng cách cân bằng tốt hơn công việc giữa các bộ xử lý, xây dựng đồng thời đa lõi và phân bổ tài nguyên hợp lý cho các tác vụ.

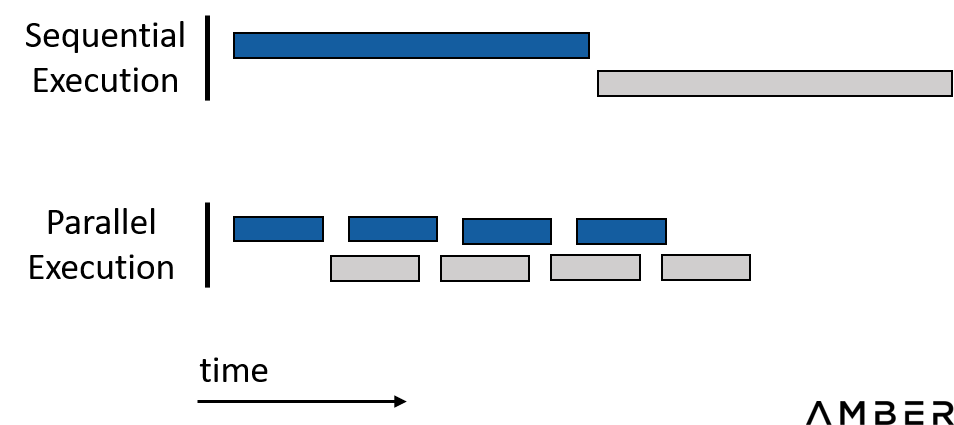

Nói tóm lại, chúng tôi muốn cố gắng hết sức để song song hóa toàn bộ quy trình làm việc. Đồng thời, quá trình thực hiện tuần tự trong đó mục sau phụ thuộc vào kết quả của mục trước nên tránh càng nhiều càng tốt.

Tiết kiệm thời gian với song song hóa

Luồng thiết kế tăng tốc GPU

3.1.1 Nhóm nhà phát triển lớn và sự thuận tiện trong phát triểnKhông giống như FPGA và ASIC, quá trình phát triển GPU không liên quan đến thiết kế phần cứng. CUDA hay OpenCL cũng có một cộng đồng nhà phát triển lớn. Các nhà phát triển có thể nhanh chóng xây dựng các phiên bản sửa đổi của riêng họ dựa trên mã nguồn mở. Ví dụ: Filecoin được phát hành trở lại vào năm 2020. Siêu quốc gia gần đây cũng đã mở nguồn tăng tốc chung của họgiải phápgiải pháp

, đây có lẽ là giải pháp nguồn mở tốt nhất thuộc loại này vào lúc này.Lợi thế này thậm chí còn rõ ràng hơn khi xem xét công việc ngoài MSM và FFT. Việc tạo bằng chứng thực sự bị chi phối bởi hai mục này, nhưng các phần khác vẫn chiếm khoảng 20% (nguồn:Sách trắng của Sin7Y

), do đó chỉ tăng tốc MSM và FFT có tác dụng hạn chế trong việc rút ngắn thời gian chứng minh. Ngay cả khi thời gian tính toán của hai mục này được nén lại ngay lập tức, thì tổng thời gian sử dụng vẫn chỉ bằng một phần năm thời gian ban đầu. Ngoài ra, vì đây là một khuôn khổ mới nổi và đang phát triển nên rất khó để dự đoán tỷ lệ này sẽ thay đổi như thế nào trong tương lai. Cho rằng FPGA cần được cấu hình lại và ASIC cũng có thể cần được thiết kế lại để sản xuất, GPU thuận tiện hơn để tăng tốc các công việc tính toán không đồng nhất.

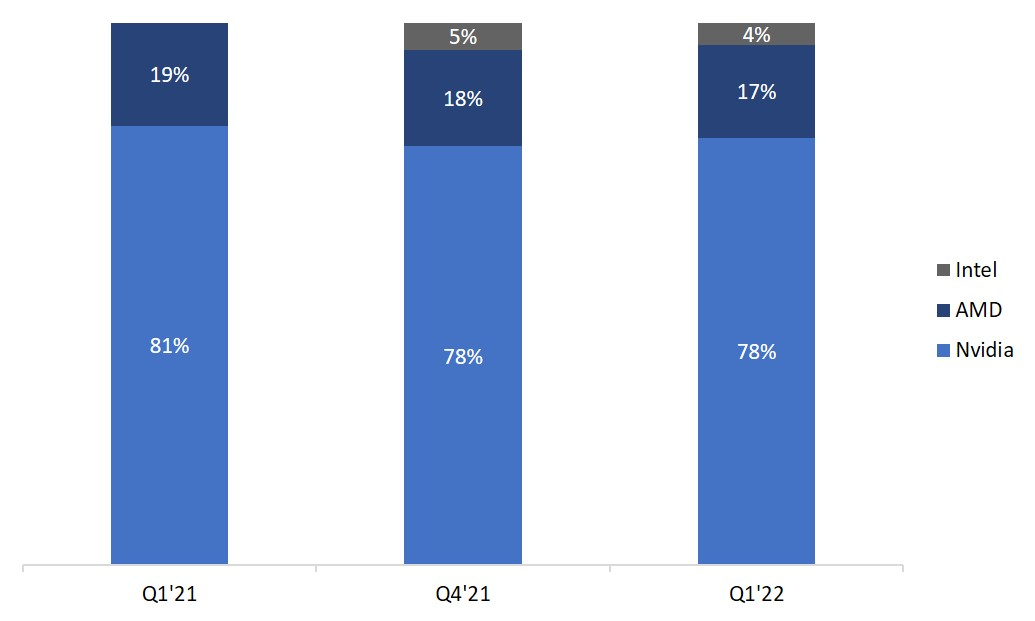

3.1.2 GPU dư thừa

thị phần chip GPU

Mô tả hình ảnh

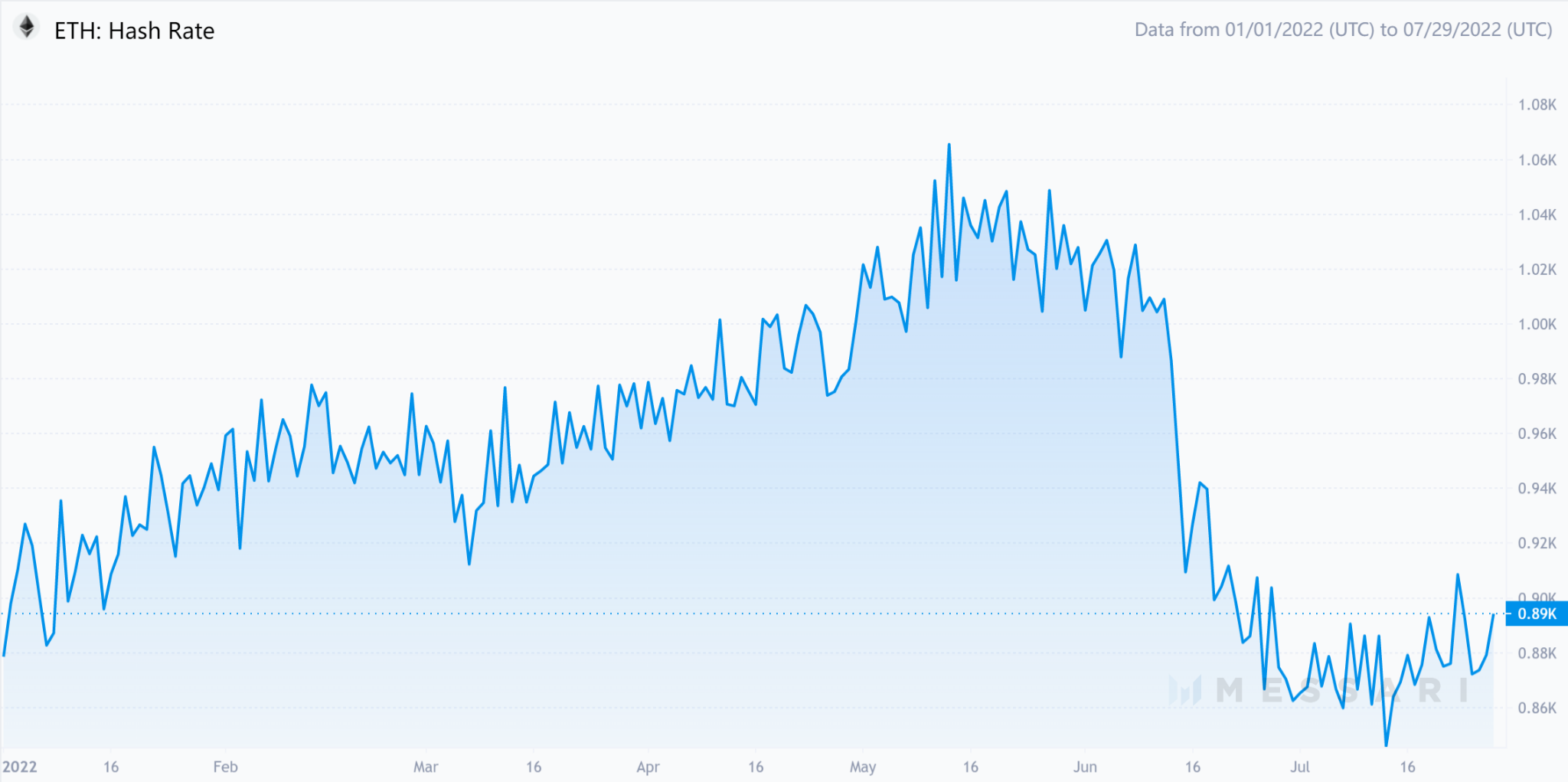

Nguồn: Nghiên cứu Jon PeddieĐặc biệt đối với khai thác, chúng tôi ước tính thận trọng ở mứcsáp nhập ethereum

Tỷ lệ băm Ethereum

Mô tả hình ảnh

Nguồn: Messari

3.2 FPGA: Cân bằng chi phí và hiệu quả

FPGA là một mạch tích hợp có cấu trúc lập trình được. Do mạch bên trong chip FPGA không được khắc cứng nên các nhà thiết kế có thể lập trình lại nó nhiều lần nếu cần. Một mặt, điều này cắt giảm hiệu quả chi phí sản xuất cao của ASIC. Mặt khác, việc sử dụng tài nguyên phần cứng của nó linh hoạt hơn so với GPU, điều này làm cho FPGA có khả năng tăng tốc và tiết kiệm năng lượng hơn nữa. Ví dụ: mặc dù có thể triển khai các FFT được tối ưu hóa trên GPU, nhưng việc thường xuyên xáo trộn dữ liệu sẽ dẫn đến một lượng lớn dữ liệu truyền giữa GPU và CPU. Tuy nhiên, việc xáo trộn không hoàn toàn ngẫu nhiên và bằng cách lập trình logic nội tại trực tiếp vào thiết kế mạch, FPGA hứa hẹn sẽ thực hiện các tác vụ nhanh hơn.

Để đạt được khả năng tăng tốc ZKP trên FPGA, vẫn cần thực hiện một số bước. Đầu tiên, việc triển khai tham chiếu của một hệ thống bằng chứng cụ thể được viết bằng C/C++ là bắt buộc. Sau đó, để mô tả các mạch logic kỹ thuật số ở mức cao hơn, việc triển khai này cần được mô tả bằng HDL (Ngôn ngữ mô tả phần cứng).

Sau đó, bạn cần mô phỏng gỡ lỗi để hiển thị dạng sóng đầu vào và đầu ra để xem mã có chạy như mong đợi hay không. Bước này là bước liên quan đến việc thực hiện nhiều nhất. Các kỹ sư không cần toàn bộ quá trình, nhưng chỉ bằng cách so sánh hai kết quả đầu ra, họ có thể xác định các lỗi nhỏ. Sau đó, một bộ tổng hợp sẽ chuyển đổi HDL thành một thiết kế mạch thực tế với các thành phần như cổng và flip-flop, đồng thời áp dụng thiết kế cho kiến trúc thiết bị và phân tích tương tự hơn. Sau khi mạch được xác nhận hoạt động bình thường, tệp lập trình cuối cùng sẽ được tạo và tải vào thiết bị FPGA.

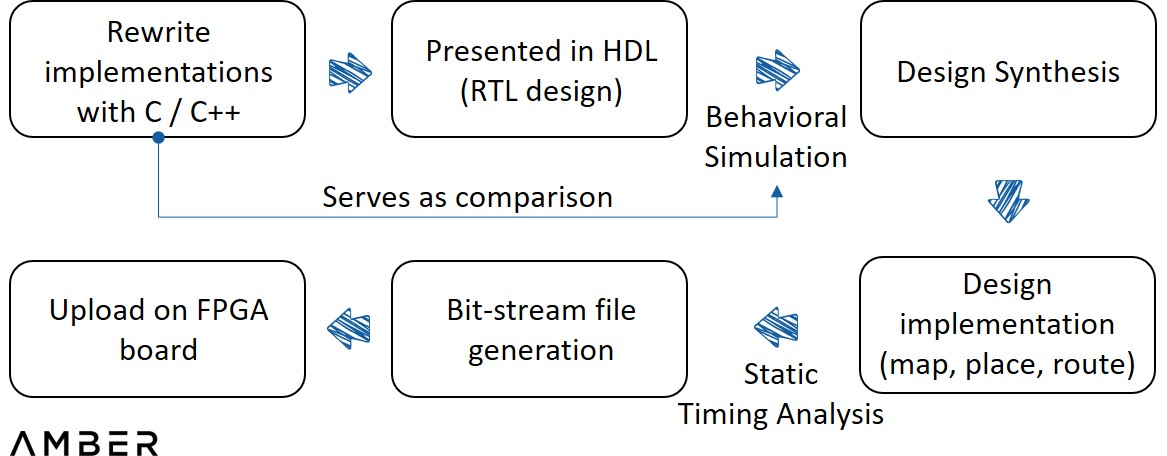

Quy trình thiết kế FPGA

3.2.1 Rào cản hiện tại và cơ sở hạ tầng chưa hoàn chỉnh

Mặc dù một số công việc tối ưu hóa mô-đun trên GPU có thể được sử dụng lại, nhưng nó cũng đối mặt với một số thách thức mới:

(1) Để bảo mật bộ nhớ cao hơn và khả năng tương thích đa nền tảng tốt hơn, hầu hết các triển khai nguồn mở không kiến thức đã được viết bằng Rust trong một thời gian dài, nhưng hầu hết các công cụ phát triển FPGA đều được viết bằng C/C++, vốn quen thuộc hơn với các kỹ sư phần cứng của. Các nhóm có thể phải viết lại hoặc biên dịch các triển khai này trước khi triển khai chúng.

(2) Khi viết các triển khai này, các kỹ sư phần mềm chỉ có thể chọn mã trong một số thư viện mã nguồn mở C/C++ hạn chế có thể được ánh xạ vào kiến trúc phần cứng thông qua hỗ trợ phát triển hiện có.

(3) Ngoài những công việc mà kỹ sư phần mềm và kỹ sư phần cứng có thể hoàn thành độc lập, họ cũng cần sự hợp tác chặt chẽ của họ để hoàn thành một số tối ưu hóa chuyên sâu. Ví dụ, một số sửa đổi về thuật toán sẽ tiết kiệm được nhiều tài nguyên phần cứng mà vẫn đảm bảo vai trò của nó như trước đây, tuy nhiên việc tối ưu hóa này dựa trên sự hiểu biết về phần cứng và phần mềm.Nói tóm lại, không giống như AI hoặc các lĩnh vực trưởng thành khác, các kỹ sư phải học và xây dựng từ đầu để đạt được khả năng tăng tốc ZKP. May mắn thay, chúng tôi đã thấy nhiều tiến bộ hơn. Ví dụ, Ingonyama tronggiấy tờ gần đây

PipeMSM được đề xuất trong , đây là một phương pháp để tăng tốc MSM trên FPGA hoặc ASIC.

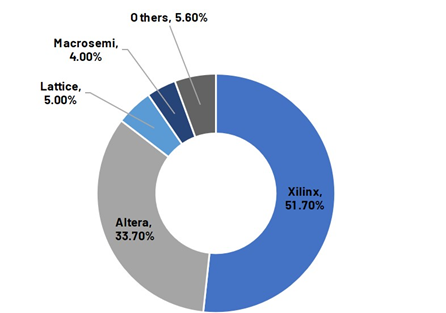

3.2.2 Thị trường độc quyền

Thị trường FPGA là một thị trường độc quyền điển hình

Mô tả hình ảnh

Nguồn: Frost & Sullivan

Các kỹ sư đã nhận ra rằng một FPGA đơn lẻ không thể cung cấp đủ tài nguyên phần cứng để tạo ZKP phức tạp, vì vậy phải sử dụng đồng thời nhiều thẻ để xác minh. Ngay cả với một thiết kế hoàn chỉnh, các dịch vụ đám mây FPGA tiêu chuẩn hiện có từ AWS và các nhà cung cấp khác cũng không lý tưởng. Ngoài ra, các công ty khởi nghiệp cung cấp giải pháp tăng tốc thường quá nhỏ để AWS hoặc các công ty khác lưu trữ phần cứng tùy chỉnh của họ và họ không có tài nguyên để chạy máy chủ của riêng mình. Có thể là lựa chọn tốt hơn khi hợp tác với các công ty khai thác lớn hoặc hợp tác với các nhà cung cấp dịch vụ đám mây gốc Web3. Tuy nhiên, mối quan hệ hợp tác có thể rất tế nhị, vì các kỹ sư nội bộ của công ty khai thác cũng có thể sẽ phát triển các giải pháp tăng tốc.

3.3 ASIC: Vũ khí tối thượng

ASIC là chip mạch tích hợp (IC) được tùy chỉnh cho các mục đích cụ thể. Thông thường, các kỹ sư vẫn sử dụng HDL để mô tả logic của ASIC theo cách tương tự như sử dụng FPGA, nhưng mạch cuối cùng được kéo cố định vào silicon, trong khi các mạch trong FPGA được tạo bằng cách kết nối hàng nghìn khối có thể định cấu hình. Thay vì tìm nguồn cung ứng phần cứng từ Nvidia, Intel hoặc AMD, các công ty phải tự quản lý toàn bộ quy trình, từ thiết kế mạch đến sản xuất và thử nghiệm. ASIC sẽ bị giới hạn ở một số chức năng nhất định, nhưng thay vào đó mang lại cho các nhà thiết kế mức độ tự do cao nhất về phân bổ tài nguyên và thiết kế mạch, vì vậy ASIC có tiềm năng lớn về hiệu suất và hiệu quả năng lượng. Các nhà thiết kế có thể loại bỏ sự lãng phí về không gian, năng lượng và chức năng bằng cách thiết kế số lượng cửa chính xác hoặc định cỡ các mô-đun khác nhau, dựa trên ứng dụng dự định.

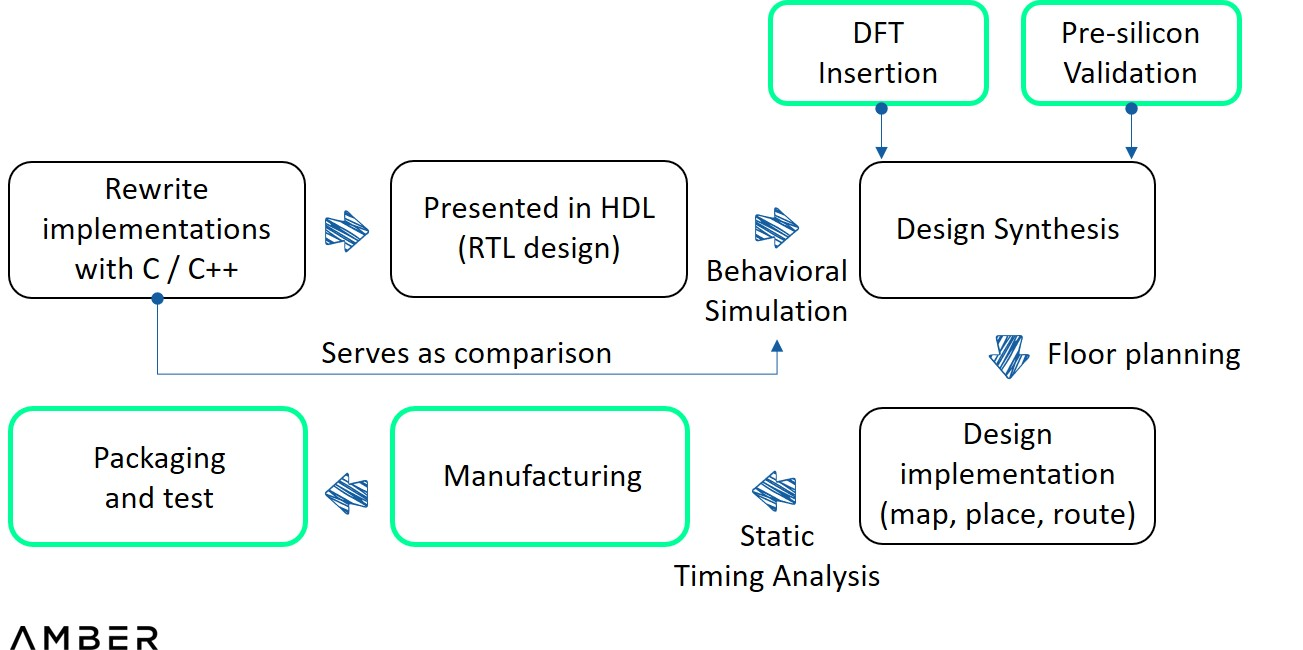

Về quy trình thiết kế, so với FPGA, ASIC cần thêm xác minh trước lát cắt (và DFT) giữa hai bước ghi và tích hợp HDL, đồng thời cần phải lập sơ đồ tầng trước khi triển khai. Cái trước là nơi các kỹ sư kiểm tra thiết kế trong môi trường ảo bằng cách sử dụng các công cụ mô phỏng phức tạp và cái sau được sử dụng để xác định kích thước, hình dạng và vị trí của các khối trong chip. Sau khi thiết kế được thực hiện, tất cả các tệp sẽ được gửi đến các xưởng đúc như TSMC hoặc Samsung để thử nghiệm. Nếu các thử nghiệm thành công, nguyên mẫu sẽ được gửi để lắp ráp và thử nghiệm.

Luồng thiết kế ASIC

3.3.1 ASIC tương đối phổ biến trong lĩnh vực không có kiến thức

Một lời chỉ trích phổ biến đối với ASIC là một khi thuật toán thay đổi, các chip trước đó hoàn toàn vô dụng, nhưng không nhất thiết phải như vậy.

Thật trùng hợp, không có công ty nào mà chúng tôi đã nói chuyện để lên kế hoạch phát triển ASIC đều tham gia vào một hệ thống hoặc dự án bằng chứng cụ thể. Thay vào đó, họ muốn phát triển một số mô-đun có thể lập trình trên ASIC, để các hệ thống bằng chứng khác nhau có thể được xử lý thông qua các mô-đun này và chỉ giao nhiệm vụ MSM và FFT cho ASIC. Điều này không phải là tối ưu cho một con chip cụ thể cho một dự án cụ thể, nhưng trong ngắn hạn, có thể tốt hơn là hy sinh hiệu suất để đạt được tính tổng quát tốt hơn là thiết kế cho một nhiệm vụ cụ thể.

3.3.1 Chi phí cao nhưng không thường xuyên

Quy trình thiết kế ASIC không chỉ phức tạp hơn nhiều so với FPGA mà quy trình sản xuất còn tiêu tốn nhiều thời gian và tiền bạc hơn. Các công ty khởi nghiệp có thể liên hệ trực tiếp với các xưởng đúc để thu âm hoặc thông qua các nhà phân phối. Có thể mất khoảng ba tháng hoặc hơn để đợi cho đến khi việc thực thi thực sự bắt đầu. Chi phí chính của tape-out đến từ mặt nạ và tấm wafer. Mặt kẻ ô được sử dụng để tạo hoa văn trên tấm wafer, là những lát silicon mỏng. Các công ty khởi nghiệp thường chọn MPW (tấm bán dẫn đa dự án), có thể chia sẻ chi phí sản xuất mặt kẻ ô và lát bán dẫn với các bên dự án khác. Tuy nhiên, tùy thuộc vào quy trình và số lượng chip mà họ chọn, chi phí loại bỏ băng được ước tính một cách thận trọng là hàng triệu đô la. Việc tháo băng cũng như lắp ráp và thử nghiệm vẫn còn vài tháng nữa. Nếu khả thi, nó cuối cùng sẽ có thể bắt đầu chuẩn bị cho sản xuất hàng loạt. Tuy nhiên, nếu có bất kỳ vấn đề gì xảy ra với quá trình kiểm tra, việc gỡ lỗi và phân tích lỗi sẽ mất một khoảng thời gian không thể đếm được và yêu cầu một lần loại bỏ khác. Từ thiết kế ban đầu đến sản xuất hàng loạt cần hàng chục triệu đô la và sẽ mất khoảng 18 tháng. Hãy an ủi rằng một phần đáng kể của những chi phí này là không thường xuyên. Ngoài ra, ASIC có hiệu suất cao và có thể tiết kiệm năng lượng và không gian, điều này rất quan trọng và giá có thể tương đối thấp.

Dưới đây chúng tôi cung cấp đánh giá chung về các giải pháp phần cứng khác nhau.

Mô tả hình ảnh

Nguồn: Hổ Phách

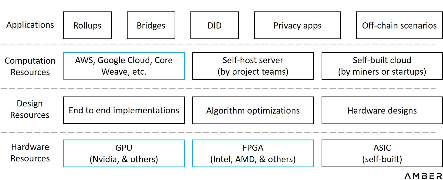

Để có được sự hiểu biết trực quan hơn về các mô hình kinh doanh có sẵn, chúng tôi đã chỉ ra tất cả những người chơi tiềm năng trên thị trường trong biểu đồ bên dưới. Vì có thể có mối quan hệ chéo hoặc sự phức tạp giữa các tác nhân, nên chúng tôi chỉ phân loại chúng theo chức năng.

Lớp chức năng tăng tốc phần cứng

Kiến thức bằng không vẫn chưa được áp dụng trên quy mô lớn và việc xây dựng các giải pháp tăng tốc sẽ là một quá trình lâu dài. Hãy cùng chờ xem bước ngoặt tiếp theo sẽ là gì. Câu hỏi quan trọng đối với các nhà xây dựng và nhà đầu tư là khi nào điểm bùng phát này sẽ đến.

Cảm ơn

Đặc biệt cảm ơn Weikeng Chen (DZK), Ye Zhang (Scroll), Kelly (Supranational) và Omer (Ingonyama) đã giúp chúng tôi hiểu tất cả các chi tiết kỹ thuật. Cũng xin cảm ơn Kai (ZKMatrix), Slobodan (Ponos), Elias và Chris (Inaccel), Heqing Hong (Accseal) và nhiều người khác đã cung cấp thông tin chuyên sâu về nghiên cứu này.

từ chối trách nhiệm

Thông tin trong tài liệu này (“Thông tin”) chỉ được cung cấp cho mục đích thông tin, ở dạng tóm tắt và không đầy đủ. Những tài liệu này không phải và không nhằm mục đích trở thành một đề nghị hoặc chào mời một đề nghị bán hoặc mua bất kỳ chứng khoán hoặc sản phẩm nào. Những thông tin như vậy không được cung cấp và không nên được coi là cung cấp lời khuyên đầu tư. Những tài liệu này không tính đến các mục tiêu đầu tư cụ thể, tình hình tài chính hoặc nhu cầu cụ thể của bất kỳ nhà đầu tư tiềm năng nào. Không có lời hứa hoặc bảo đảm nào, rõ ràng hay ngụ ý, được đưa ra liên quan đến tính công bằng, đúng đắn, chính xác, hợp lý hoặc đầy đủ của Tài liệu. Chúng tôi không cam kết cập nhật tài liệu này. Các nhà đầu tư tiềm năng không nên coi nó như một sự thay thế cho đánh giá hoặc nghiên cứu của chính họ. Các nhà đầu tư tiềm năng nên tham khảo ý kiến của các cố vấn pháp lý, quy định, thuế, kinh doanh, đầu tư, tài chính và kế toán của riêng họ trong phạm vi họ cho là cần thiết và đưa ra bất kỳ quyết định đầu tư nào dựa trên phán đoán của chính họ và lời khuyên của cố vấn.

liên kết gốc